Des émetteurs en grandes ondes émettent des signaux horaires à un rythme très faible (1 bit par seconde).

Les émetteurs disponibles en Europe sont

Les 2 derniers sont réputés accessibles en France et utilisent un codage similaire.

Il y avait un émetteur en Suisse (HBG Prangis 75 kHz - 1966) qui a cessé d'émettre en fin 2011.

|

|

L'émetteur situé à Allouis (dans le Cher, à peu prés au centre de la France) développe une puissance de 2 MW dans la journée et 1 MW dans la nuit (0 à 6h) pour la radiodiffusion en AM de France-Inter. Les signaux horaires sont diffusés en PM. Sa disponibilité est excellente, une interruption de maintenance périodique le mardi entre 0 et 5 heures. L'émetteur DCF77, situé à Mainflingen (près de Frankfort, Allemagne) développe 50 kW et est uniquement consacré à l'émission de signaux horaires en AM. Sa disponibilité est excellente, quelques interruptions en cas d'orage. |

|

Le champ utile est très fort sur toute la France, le point le plus faible étant l'est de la Corse avec 0.5mV/m.

|

|

|

Les deux émetteurs utilisent le même code horaire, mais ils l'expriment en utilisant un codage différent ; la modulation du DCF77 est en amplitude, celle de France Inter est en phase (ou en fréquence). La modulation de phase est de +/- 1 radian, avec une pente de +/- 40

rd/s, soit +/- 6.36 Hz. A chaque seconde, on transmet un bit 0 avec un

aller retour simple, et un bit 1 avec un aller retour double en phase.

Les deux premieres tranches sont pour les info horaires, les 7 suivantes

pour des données numériques (non utilisées), la dernière

tranche de la seconde n'est jamais modulée pour permettre la synchronisation. |

|

|

Le tableau ci-joint détaille la composition du message (cliquer dessus pour agrandir). Dans les 2 systèmes, la seconde 59 n'est jamais modulée pour permettre la synchronisation. Cette pause dure au moins de 58.850 jusqu'à 59.950, soit un silence de 1100 ms. On dispose ainsi de 59 bits d'information, dont seulement 42 sont utilisés. Les bits des secondes 0 à 15 inclus sont utilisé pour des informations internes sans rapports avec l'heure ou la date. Les champs principaux sont protégés par une parité paire, c'est à dire que la somme de tous les bits du champs y compris la parité doit être paire. Le message codé indique l'heure valide à la seconde suivante, par exemple si un message transmet 22:00, il sera 22h00 à la minute suivante. |

Une bonne réception, sensible et sélective oblige à utiliser un récepteur superhétérodyne.

La fréquence intermédiaire doit être faible afin d'avoir le maximum de déviation. Mais si on veut maintenir la fréquence image au delà des bandes latérales du canal standard (+/- 4500 Hz), la fréquence locale ne doit pas être comprise entre 160kHz et 164kHz.

|

|

Deux solutions simples :

|

Détermination de la bande passante fréquence intermédiaire :

Si on veut rester dans 0/-3 dB, on doit avoir

Dans tous les cas, nous savons que la sélectivité de l'étage d'entrée est fondamentale, nous utiliserons un circuit accordé amplifié par un FET. Le gain est de l'ordre de 10dB.

Le mélangeur est un amplificateur différentiel, chargé par un cricuit accordé sur Fint. A ces fréquences là, il est intéressant d'utiliser une simulation d'inductance basée sur Q5, avec un Q de l'ordre de 5, et un Zmax voisin de 30k. L'amplificateur différentiel est piloté par un courant moyen dans Q3 de 1mA, modulé avec +/- 100µA, et on récupère près de 100mVcàc à la fréquence intermédiaire sur le collecteur de Q1 avec 5mVeff à l'entrée, soit plus de 25dB de gain. On peut monter l'injection de 160kHz, en baissant R7, par exemple aller jusqu'à 4.7k, ce qui module le courant Q3 à +/- 800µA. On fera attention à la tension base Q1 générée par la variation de Ib Q1.

A la suite de l'étage mélangeur, on devra amplifier la fréquence intermédiaire et encore atténuer les fréquences proches de 160kHz. On utilise un filtre actif à source controllée, dont le gain est juste inférieur à 2 pour ne pas osciller. Le gain devrait être meilleur que 20dB à Fint et l'atténuation meilleure que 30dB à 160kHz.

Noter que R6a est réduite pour tenir compte de l'impédance de sortie du mélangeur (31k).

|

Sortie du filtre actif avec 1mVeff à l'entrée |

Le courant Q3, modulé par le 160kHz avec R7=47k |

Nous voulons faire une détection de fréquence ou de phase. La meilleure solution est d'utiliser une boucle de phase (PLL).

Le VCO doit avoir une plage de capture extremement faible, car sinon, à la mise en route, il n'y aura jamais de signal en sortie du filtre 2kHz. On peut parler d'une plage de capture de l'ordre de +/-200 Hz autour de 160kHz soit de l'ordre de 0.1%. Avec de telles valeurs, un VCO analogique (4046, 567) n'est pas adéquat, et seul un VCXO peut garantir cette très faible plage de capture.

Pour que la réalisation soit plus simple, on définit un VXCO basé sur un quartz 10.240 MHz en mode parallèle, avec 2 diodes varicap et un circuit HC4060. Un première division par 64 et on obtient la fréquence de 160 kHz, une division par 8 puis par 10 et on obtient le 2kHz.

Un tel VCXO a un transfert très faible de l'ordre de Kv=90 Hz/V. On règlera le VCXO pour avoir 159998 Hz avec une tension de 0V et 160002 Hz pour 5 V.

La détecteur de phase 1, simple porte XOR est intrinsèquement sensible au rapport cyclique, caractéristique qui n'est pas forcément propre à la sortie du filtre passe bande, ni surtout à la sortie du diviseur par 10.

La boucle est donc construite avec la comparateur de phase sensible aux fronts (le comparateur 2 d'un 4046) insensible au rapport cyclique, et dont la phase de capture est 0° et un tranfert Kp=0.8 V/rd.

L'entrée de la PLL, broche 14, peut être couplée par un condensateur à la sortie du filtre 2kHz, et nécessite 400mV crête à crête.

La fréquence naturelle de la boucle doit être choisie très bas, bien en dessous de la fréquence de modulation en phase que l'on veut détecter, c'est à dire 20 Hz. On visera des constantes de temps qui s'expriment en secondes ; dans ce cas le choix des composants n'est pas libre, en particulier la résistance de fuite de la capacité risque d'amener un décalage constant de la phase. On choisira une capacité pas trop élevée, avec une très forte tension d'utilisation (63V). De la même façon, la résistance R1 ne peut pas être trop grande car l'entrée du VCO a une impédance propre (fuite des varicap), mais surtout pour limiter les risques de pollutions extérieures sur un circuit à trés haute impédance.

|

|

Le filtre de boucle est au minimum un RC amorti avec les équations suivantes :

Pour une fréquence naturelle de l'ordre de 30 mHz et Q=pas trop fort, on choisit :

Cette PLL devrait mettre quelques secondes pour accrocher. |

Pour diminuer le bruit injecté dans le VCO à cause de la fréquence de comparaison, on installe un troisième pole avec une capacité derrière le filtre principal, à une fréquence de l'ordre de 10Hz pour ne pas perturber le transfert de la boucle.

Le tansfert final est donné ci dessous, la marge de phase est bonne.

La sortie "phase comp 1" (pin 2), et la sortie d'une porte OU exclusif. La phase de vérouillage étant 0°, cette sortie est normallement à 0 avec des pulses positifs à 4000Hz. Si les signaux ont le même rapport cyclique, cette sortie peut être utilisée, ce n'est pas le cas ici.

La sortie "phase pulse" (pin 1) est normalement à 1 mais toute modulation de phase autour de ce point va provoquer l'apparition de pulses négatifs dont la valeur moyenne est de Vdd-Vdd*phase/2pi et dont la fréquence est 2000Hz. Dans notre cas avec +/- 1 radian sous 5 Volts, on aura un signal de 5V à 4.2V, quelque soit le sens de la modulation. On peut dire que ce type de détecteur redresse la modulation de phase.

La détection des pulse se fera avec un transistor qui va détecter les pulses en dessous de Vcc-0.5V. Il faut prévoir un peu d'hystérésis pour éliminer les multiples commutations sur les résidus de 2kHz. Les pulses en sortie sont compris entre 20 et 30ms.

Cette sortie peut aussi servir de détecteur d'accrochage. En effet, lorsque la PLL est accrochée, la valeur moyenne de ce signal est supérieure à Vcc-0.8V. Il suffit de comparer cette valeur moyenne à un seuil supérieur à 0.8V pour disposer d'un signal qui va remettre à zéro une tempo de 25sec. Si la tempo arrive à terme sans reset intermédiaire, on considère que la PLL est accrochée.

Le VCO de la PLL 4046 est utilisé pour convertir en fréquence la force du signal reçu avec un transfert de l'ordre de 50 Hz/Vcrete. Ce signal fréquenciel est facile à mesurer avec un µcontrolleur ou un PC voire à écouter avec un écouteur, et permet ainsi simplement de régler l'antenne.

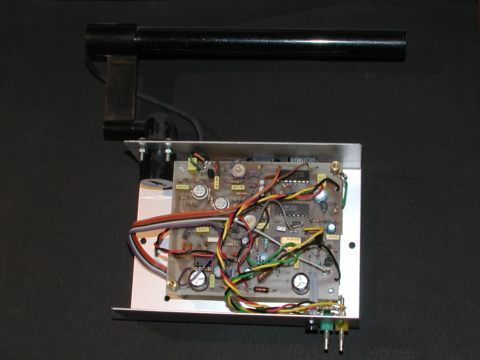

L'interface est réalisée sur le port parallèle LPT.

La liste des connexions dans l'ordre des cables sur la prise RJ45 :

| Signal | couleur cable interne | couleur cable externe | pin DB25 | Registre status @(LPT+1) | signal LPT |

| 640 kHz | orange | marron | |||

| +5V | rouge | bleu | 11 | -S7 | busy |

| 0 Volt | noir | jaune | 18 | gnd | |

| 2500 Hz | marron | vert | 10 | +S6 | ack |

| 0 Volt | noir | rouge | 25 | gnd | |

| /PPulse | blanc | noir | 12 | +S5 | paper out |

| /Verrouillé | violet | violet | 13 | +S4 | select |

| SFreq | gris | gris | 15 | +S3 | error |

D'abord, on vérifie qu'il y a de l'activité sur la ligne PPulse, en attendant successivement les transitions 1>0 puis 0>1 et ceci 2 fois.

Le point de départ est la détection de fin de minute. Il n'y a aucune modulation pendant au moins 1 seconde. Cette détection est réalisée par un timer remis à zéro à transition détectée. Avant de remettre à zéro, le timer est lu. Si le temps est supérieur à 1 seconde, nous sommes sur la seconde zéro.

A ce moment on enclenche une boucle sur les 59 prochaines secondes (0 à 58)

On attend la première transition 1>0, on démarre un timer, et on attend la transition 0>1. C'est la première impulsion négative de la seconde, on prend la moitié de cette impulsion comme temps 0.

Ensuite on échantillone la ligne PPulse à chaque fois que le temps écoulé depuis le temps 0 passe par un multiple de 50ms. L'échantillonage est fait plusieurs fois successivement pour pouvoir faire un vote majoritaire, et être robuste à des impulsions parasites. Ce processus est fait 19 fois (de +50ms à +950ms). A la fin de la seconde on dispose de tout ce qui faut pour décider si on a un bit 0 ou 1 ou une indeterminée.

A la fin de la boucle de 0 à 58 secondes, lors de la pause, on a suffisamment de temps pour décoder les 59 bits et mettre à disposition l'heure qui sera valide à la seconde 0 suivante.

Et on reprend à la détection de fin de minute.

Exemple de sortie d'un programme réalisé sour DOS :